# **SAF3560**

# Terrestrial digital radio processor

Rev. 03 — 15 September 2010

**Product short data sheet**

# 1. General description

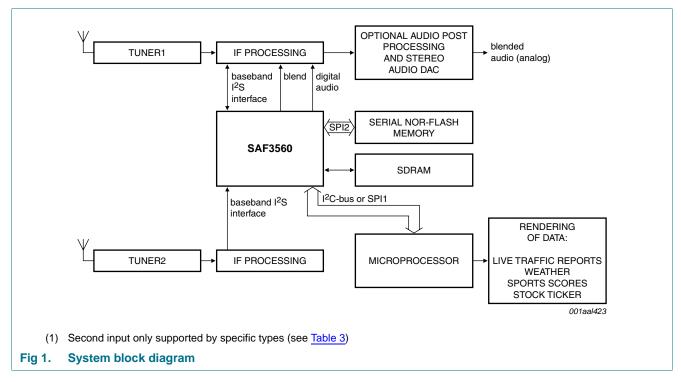

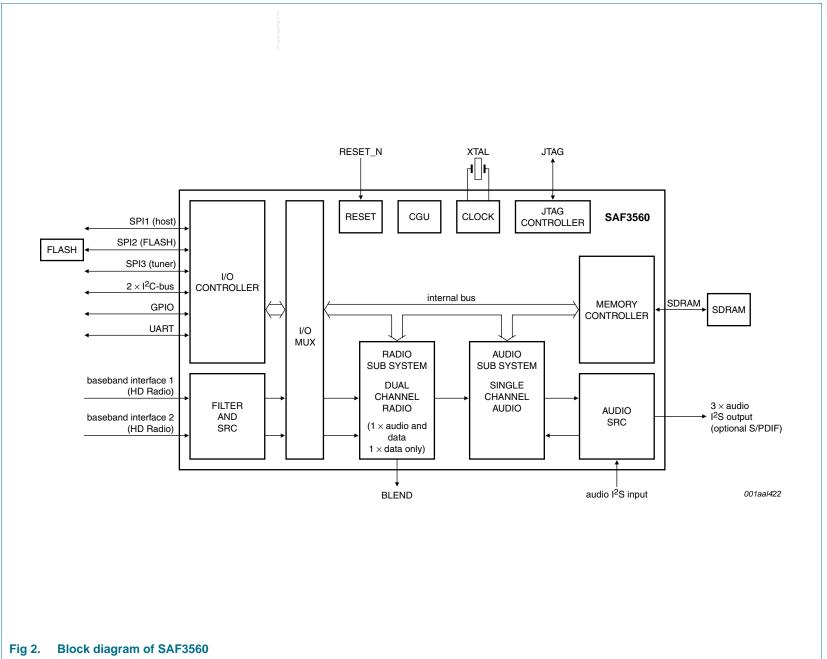

The SAF3560 is a digital radio processor that demodulates and processes digital terrestrial baseband signals, such as HD Radio signals, into audio signals and digital data signals.

Major benefits of terrestrial radio processor systems with SAF3560 are:

- · Compatibility with conventional baseband radio reception ICs

- Dramatically improved reception and sound quality

- CD-sound quality without noise, interference and multipath fading for FM

- Providing new data services

- HD Radio reception including audio processing

- Voltage partitioning of I/Os

#### Terrestrial digital radio processor

System designers can add digital terrestrial radio capability in a simple and inexpensive way through the SAF3560. The SAF3560 decodes digital radio input to provide digital audio and also processes digital data. Multiple interfaces give flexibility while integrating the SAF3560 into the receiver system.

## 2. Features and benefits

# 2.1 HD Radio technology

- HD Radio signal decoding for AM and FM digital audio

- Dual HD Radio support for support of 2nd station for background scanning and data service

- Front-end to baseband interface support through serial baseband I<sup>2</sup>S-bus type interface

- Secondary baseband interface for dual tuner applications

- Metadata support for HD Radio reception

- Data services support for HD Radio reception

- Advanced HD Radio feature support, such as<sup>1</sup>:

- Conditional Access (CA)

- Store and replay

- Apple ID3 tag

- Multicasting

- Electronic Program Guide (EPG)

## 2.2 Digital audio

- Up to 6 channel (5.1) audio support through I<sup>2</sup>S-bus serial audio interface

- Optional SRC (8 kHz to 48 kHz) for up to 6 channels of I<sup>2</sup>S-bus audio output

- I<sup>2</sup>S-bus serial audio input for auxiliary processing

- Optional SRC (8 kHz to 48 kHz) for I<sup>2</sup>S-bus input

- Optional restricted support for 96 kHz input and output sample-rate conversion

- Optional digital audio output through S/PDIF (without SRC)

- Basic audio processing for external digital audio sources

- Advanced audio processing (please contact NXP for a list of supported audio processing features: Section 14 "Contact information")

#### 2.3 Memory

- Supports SDR-SDRAM controller (up to 512 Mbit in 16-bit configuration)

- Supports serial NOR-Flash memory with various sizes depending on the actual application

SAF3560\_SDS

All information provided in this document is subject to legal disclaimers.

<sup>1.</sup> Please contact NXP for a detailed list of supported feature sets: Section 14 "Contact information".

# Terrestrial digital radio processor

# 2.4 Other peripheral interfaces

- Two I<sup>2</sup>C-bus interfaces

- Three Serial Peripheral Interfaces (SPI)

- One UART interface

- Five individual GPIO pins for applications and diagnostics

- One JTAG interface for diagnostics

## 2.5 Miscellaneous

- One internal clock oscillator and two internal Phase-Locked Loops (PLL)

- Powerful signal and audio processing core architecture

- Qualified in accordance with AEC-Q100

# 3. Quick reference data

Table 1. Power supply characteristics

After power-up the SAF3560 needs a reset pulse for at least 2 ms.

|                              | <del>-</del>                                   |                         |            |      |     |      |      |

|------------------------------|------------------------------------------------|-------------------------|------------|------|-----|------|------|

| Symbol                       | Parameter                                      | Conditions              |            | Min  | Тур | Max  | Unit |

| Supply voltages              |                                                |                         |            |      |     |      |      |

| V <sub>DDA(OSC)(1V2)</sub>   | oscillator analog supply voltage (1.2 V)       |                         |            | 1.14 | 1.2 | 1.32 | V    |

| V <sub>DDA(PLL)(1V2)</sub>   | PLL analog supply voltage (1.2 V)              |                         |            | 1.14 | 1.2 | 1.32 | V    |

| V <sub>DDD(C)(1V2)</sub>     | core digital supply voltage (1.2 V)            |                         |            | 1.14 | 1.2 | 1.32 | V    |

| V <sub>DDD(DAB)(3V3)</sub>   | DAB digital supply voltage (3.3 V)             |                         |            | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DDD(DSP)(3V3)</sub>   | DSP digital supply voltage (3.3 V)             |                         |            | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DDD(JTAG)(3V3)</sub>  | JTAG digital supply voltage (3.3 V)            |                         |            | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DDD(MC)(3V3)</sub>    | microcontroller digital supply voltage (3.3 V) |                         |            | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DDD(MEM)(1V2)</sub>   | memory digital supply voltage (1.2 V)          |                         |            | 1.14 | 1.2 | 1.32 | V    |

| V <sub>DDD(SDRAM)(3V3)</sub> | SDRAM digital supply voltage (3.3 V)           |                         |            | 3.0  | 3.3 | 3.6  | V    |

| Supply currents              |                                                |                         |            |      |     |      |      |

| I <sub>DD</sub>              | supply current                                 | all core related blocks | <u>[1]</u> | -    | 90  | 116  | mΑ   |

|                              |                                                | all I/O related blocks  | [2]        | -    | 28  | 37   | mΑ   |

| Power dissipation            | on                                             |                         |            |      |     |      |      |

| P <sub>tot</sub>             | total power dissipation                        |                         |            | -    | 0.2 | 0.5  | W    |

$<sup>[1] \</sup>quad Through pins \ V_{DDA(OSC)(1V2)}, \ V_{DDA(PLL)(1V2)}, \ V_{DDD(C)(1V2)} \ and \ V_{DDD(MEM)(1V2)}.$

$<sup>[2] \</sup>quad \text{Through pins $V_{DDD(DAB)(3V3)}$, $V_{DDD(DSP)(3V3)}$, $V_{DDD(JTAG)(3V3)}$, $V_{DDD(MC)(3V3)}$ and $V_{DDD(SDRAM)(3V3)}$.}$

# Terrestrial digital radio processor

# 4. Ordering information

# Table 2. Ordering information

| Type number     | Package  |                                                                                                                         |          |  |  |  |

|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                 | Name     | Description                                                                                                             | Version  |  |  |  |

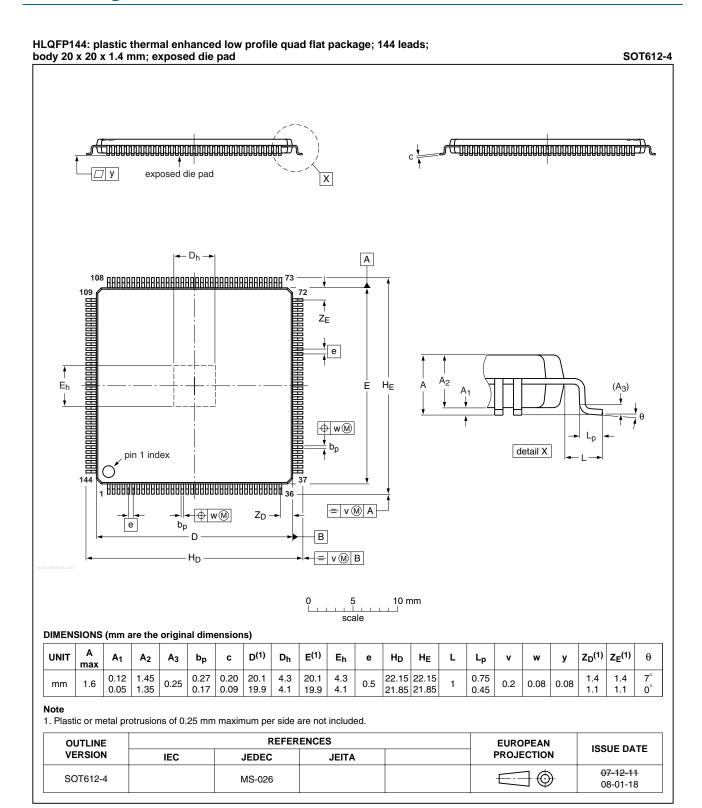

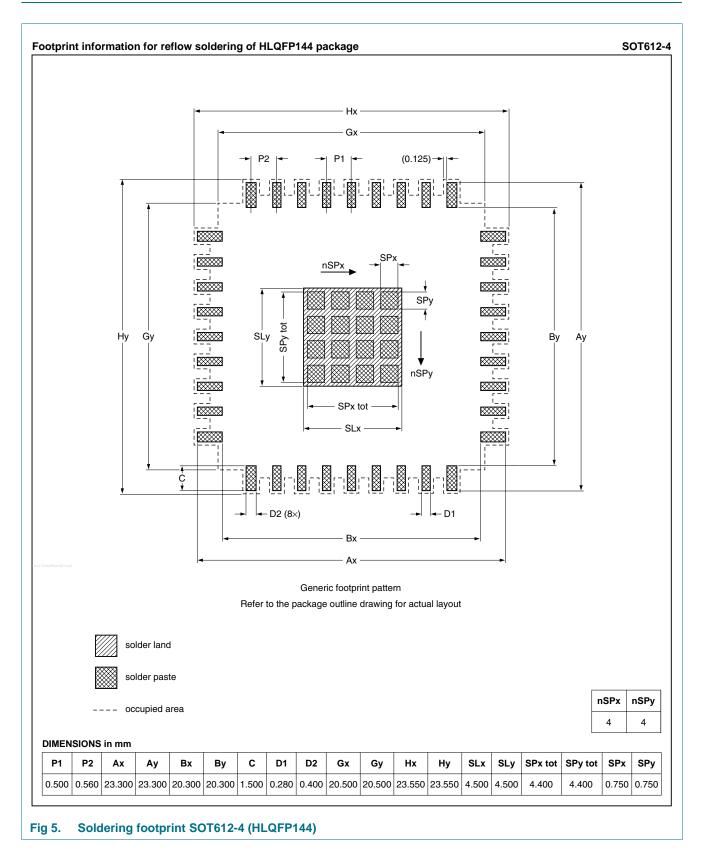

| SAF3560HV/V1100 | HLQFP144 | plastic thermal enhanced low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm; exposed die pad   | SOT612-4 |  |  |  |

| SAF3560HV/V1101 | HLQFP144 | plastic thermal enhanced low profile quad flat package; 144 leads; body 20 $\times$ 20 $\times$ 1.4 mm; exposed die pad | SOT612-4 |  |  |  |

| SAF3560HV/V1102 | HLQFP144 | plastic thermal enhanced low profile quad flat package; 144 leads; body 20 $\times$ 20 $\times$ 1.4 mm; exposed die pad | SOT612-4 |  |  |  |

| SAF3560HV/V1103 | HLQFP144 | plastic thermal enhanced low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm; exposed die pad   | SOT612-4 |  |  |  |

## Table 3. Main applications

| Type number     | Main application                       | Option       |

|-----------------|----------------------------------------|--------------|

| SAF3560HV/V1100 | HD Radio 1.0                           | single tuner |

| SAF3560HV/V1101 | HD Radio 1.0 + Conditional Access (CA) | single tuner |

| SAF3560HV/V1102 | HD Radio 1.5                           | dual tuner   |

| SAF3560HV/V1103 | HD Radio 1.5 + Conditional Access (CA) | dual tuner   |

Terrestrial digital radio processor

# 5 Block diagram

All information provided in this document is subject to legal disclaimers

SAF3560\_SDS

Product short data sheet

Terrestrial digital radio processor

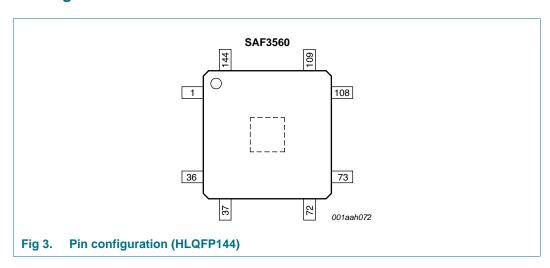

# 6. Pinning information

# 6.1 Pinning

Table 4. Pin allocation table (HLQFP144)

| Pin | Symbol                       | Pin | Symbol                       | Pin | Symbol                   | Pin | Symbol                |

|-----|------------------------------|-----|------------------------------|-----|--------------------------|-----|-----------------------|

| 1   | CLKOUT                       | 2   | RESET_N                      | 3   | I2C1_SCL                 | 4   | I2C1_SDA              |

| 5   | I2C1_DA                      | 6   | V <sub>DDD(MC)(3V3)</sub>    | 7   | I2C2_SCL                 | 8   | I2C2_SDA              |

| 9   | I2C2_DA                      | 10  | SPI1_SO                      | 11  | SPI1_SI                  | 12  | SPI1_SCLK             |

| 13  | SPI1_SS_N                    | 14  | $V_{DDD(C)(1V2)}$            | 15  | $V_{DDD(MC)(3V3)}$       | 16  | SPI2_MI               |

| 17  | SPI2_MO                      | 18  | SPI2_SCLK                    | 19  | SPI2_SS1_N               | 20  | SPI2_SS2_N            |

| 21  | $V_{\text{DDD(MC)(3V3)}}$    | 22  | SPI2_SS3_N                   | 23  | SPI2_SS4_N               | 24  | UART_TD               |

| 25  | UART_RD                      | 26  | UART_RTS                     | 27  | $V_{DDD(C)(1V2)}$        | 28  | $V_{DDD(MC)(3V3)}$    |

| 29  | UART_CTS                     | 30  | SPI3_MISO                    | 31  | SPI3_MOSI                | 32  | SPI3_SCLK             |

| 33  | SPI3_SS1_N                   | 34  | $V_{DDD(DAB)(3V3)}$          | 35  | SPI3_SS2_N               | 36  | GPIO0                 |

| 37  | GPIO1                        | 38  | GPIO2                        | 39  | GPIO3                    | 40  | GPIO4                 |

| 41  | - <u>[1]</u>                 | 42  | $V_{DDD(DAB)(3V3)}$          | 43  | -                        | 44  | -                     |

| 45  | -                            | 46  | -                            | 47  | -                        | 48  | -                     |

| 49  | -                            | 50  | -                            | 51  | -                        | 52  | -                     |

| 53  | -                            | 54  | -                            | 55  | BB1_I2S_BCK              | 56  | BB1_I2S_WS            |

| 57  | BB1_I2S_I                    | 58  | BB1_I2S_Q                    | 59  | BB2_I2S_BCK              | 60  | BB2_I2S_WS            |

| 61  | BB2_I2S_I                    | 62  | BB2_I2S_Q                    | 63  | $V_{DDD(C)(1V2)}$        | 64  | $V_{DDD(DSP)(3V3)}$   |

| 65  | HBCKOUT                      | 66  | I2S1_O_BCK                   | 67  | I2S1_O_WS                | 68  | I2S1_O_SD             |

| 69  | BLEND                        | 70  | $V_{\text{DDD(MEM)(1V2)}}$   | 71  | $V_{DDD(DSP)(3V3)}$      | 72  | I2S2_O_SD             |

| 73  | I2S3_O_SD/<br>SPDIF_O        | 74  | I2S_I_WS                     | 75  | I2S_I_BCK                | 76  | I2S_I_SD              |

| 77  | SDRAM_DIO0                   | 78  | SDRAM_DIO1                   | 79  | SDRAM_DIO2               | 80  | $V_{DDD(SDRAM)(3V3)}$ |

| 81  | SDRAM_DIO3                   | 82  | SDRAM_DIO4                   | 83  | SDRAM_DIO5               | 84  | SDRAM_DIO6            |

| 85  | V <sub>DDD(SDRAM)(3V3)</sub> | 86  | SDRAM_DIO7                   | 87  | SDRAM_DIO8               | 88  | SDRAM_DIO9            |

| 89  | SDRAM_DIO10                  | 90  | V <sub>DDD(SDRAM)(3V3)</sub> | 91  | V <sub>DDD(C)(1V2)</sub> | 92  | SDRAM_DIO11           |

# Terrestrial digital radio processor

Table 4.

Pin allocation table (HLQFP144) ...continued

| Pin | Symbol                       | Pin | Symbol                       | Pin | Symbol                     | Pin | Symbol                       |

|-----|------------------------------|-----|------------------------------|-----|----------------------------|-----|------------------------------|

| 93  | SDRAM_DIO12                  | 94  | SDRAM_DIO13                  | 95  | SDRAM_DIO14                | 96  | V <sub>DDD(SDRAM)(3V3)</sub> |

| 97  | SDRAM_DIO15                  | 98  | SDRAM_WE_N                   | 99  | SDRAM_DQM0                 | 100 | SDRAM_DQM1                   |

| 101 | $V_{DDD(SDRAM)(3V3)}$        | 102 | $V_{\text{DDD(MEM)(1V2)}}$   | 103 | SDRAM_BA0                  | 104 | SDRAM_BA1                    |

| 105 | SDRAM_CS_N                   | 106 | SDRAM_RAS_N                  | 107 | $V_{DDD(SDRAM)(3V3)}$      | 108 | SDRAM_CAS_N                  |

| 109 | SDRAM_CLKE                   | 110 | SDRAM_AO0                    | 111 | SDRAM_AO1                  | 112 | $V_{DDD(SDRAM)(3V3)}$        |

| 113 | SDRAM_AO2                    | 114 | SDRAM_AO3                    | 115 | SDRAM_AO4                  | 116 | $V_{DDD(SDRAM)(3V3)}$        |

| 117 | SDRAM_AO5                    | 118 | SDRAM_AO6                    | 119 | SDRAM_AO7                  | 120 | SDRAM_AO8                    |

| 121 | SDRAM_AO9                    | 122 | V <sub>DDD(SDRAM)(3V3)</sub> | 123 | SDRAM_AO10                 | 124 | V <sub>DDD(C)(1V2)</sub>     |

| 125 | SDRAM_AO11                   | 126 | SDRAM_AO12                   | 127 | SDRAM_CLK                  | 128 | SDRAM_CLKIN                  |

| 129 | V <sub>DDD(SDRAM)(3V3)</sub> | 130 | V <sub>SS</sub> [2]          | 131 | TRST_N                     | 132 | TCK                          |

| 133 | TMS                          | 134 | V <sub>DDD(C)(1V2)</sub>     | 135 | TDI                        | 136 | TDO                          |

| 137 | V <sub>SS</sub> [2]          | 138 | V <sub>DDD(JTAG)(3V3)</sub>  | 139 | V <sub>DDA(PLL)(1V2)</sub> | 140 | V <sub>DDA(OSC)(1V2)</sub>   |

| 141 | XTALI                        | 142 | XTALO                        | 143 | $V_{\text{DDD(MEM)(1V2)}}$ | 144 | V <sub>SS</sub> [2]          |

<sup>[1]</sup> See Table 14 for unused pins.

# 6.2 Pin description

Table 5. Pin description overview

| Pin category                                 | Details                                         | Table number |

|----------------------------------------------|-------------------------------------------------|--------------|

| Power supply pins                            | analog and digital supply pins                  | Table 6      |

| Baseband interface pins                      | baseband and audio pins (I <sup>2</sup> S-bus)  | Table 7      |

| Generic interface pins                       | GPIO and SPI3 pins                              | Table 8      |

| SDRAM interface pins                         | data, address and control pins                  | Table 9      |

| Serial NOR-Flash interface pins              | SPI2 pins                                       | Table 10     |

| External host microcontroller interface pins | SPI1, I2C1, I2C2, UART, CLKOUT and RESET_N pins | Table 11     |

| JTAG interface pins                          | JTAG pins                                       | Table 12     |

| Crystal oscillator pins                      | XTALI and XTALO pins                            | Table 13     |

Table 6. Pin description (power supplies)

| Symbol                     | Pin                                | Type[1] | Description                              |  |  |  |

|----------------------------|------------------------------------|---------|------------------------------------------|--|--|--|

| Global ground              | supply                             |         |                                          |  |  |  |

| V <sub>SS</sub>            | 130, 137, 144 and backside contact | G       | analog and digital global ground supply  |  |  |  |

| Analog supplies            |                                    |         |                                          |  |  |  |

| V <sub>DDA(OSC)(1V2)</sub> | 140                                | Р       | oscillator analog supply voltage (1.2 V) |  |  |  |

| V <sub>DDA(PLL)(1V2)</sub> | 139                                | Р       | PLL analog supply voltage (1.2 V)        |  |  |  |

| Digital supplies           |                                    |         |                                          |  |  |  |

| V <sub>DDD(C)(1V2)</sub>   | 14, 27, 63, 91, 124 and<br>134     | Р       | core digital supply voltage (1.2 V)      |  |  |  |

| V <sub>DDD(DAB)(3V3)</sub> | 34 and 42                          | Р       | DAB digital supply voltage (3.3 V)       |  |  |  |

<sup>[2]</sup> Global V<sub>SS</sub> pin at backside contact

Table 6. Pin description (power supplies) ... continued

| Symbol                        | Pin                                             | Type[1] | Description                                    |

|-------------------------------|-------------------------------------------------|---------|------------------------------------------------|

| $V_{DDD(DSP)(3V3)}$           | 64 and 71                                       | Р       | DSP digital supply voltage (3.3 V)             |

| V <sub>DDD(JTAG)(3V3)</sub>   | 138                                             | Р       | JTAG digital supply voltage (3.3 V)            |

| V <sub>DDD(MC)(3V3)</sub>     | 6, 15, 21 and 28                                | Р       | microcontroller digital supply voltage (3.3 V) |

| V <sub>DDD</sub> (SDRAM)(3V3) | 80, 85, 90, 96, 101, 107, 112, 116, 122 and 129 | Р       | SDRAM digital supply voltage (3.3 V)           |

| $V_{\text{DDD(MEM)(1V2)}}$    | 70, 102 and 143                                 | Р       | memory digital supply voltage (1.2 V)          |

<sup>[1]</sup> Table 15 defines the pin type.

Table 7. Pin description (baseband interface)

| Table 7. I in description (baseband interrace) |      |                     |                                                                                                                              |  |

|------------------------------------------------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                                         | Pin  | Type <sup>[1]</sup> | Description                                                                                                                  |  |

| Baseband inter                                 | face |                     |                                                                                                                              |  |

| BB1_I2S_BCK                                    | 55   | IOZU-H              | bit clock input and output of first baseband interface                                                                       |  |

| BB1_I2S_I                                      | 57   | IZU-H               | I data input line of first baseband interface                                                                                |  |

| BB1_I2S_Q                                      | 58   | IZU-H               | Q data input line of first baseband interface                                                                                |  |

| BB1_I2S_WS                                     | 56   | IOZU-H              | word select input and output line of first baseband interface                                                                |  |

| BLEND                                          | 69   | OL                  | blend indicator output,<br>HIGH = digital audio / LOW = analog radio <sup>[2]</sup>                                          |  |

| BB2_I2S_BCK                                    | 59   | IOZU-H              | bit clock input and output of second baseband interface                                                                      |  |

| BB2_I2S_I                                      | 61   | IZU-H               | I data input line of second baseband interface                                                                               |  |

| BB2_I2S_Q                                      | 62   | IZU-H               | Q data input line of second baseband interface                                                                               |  |

| BB2_I2S_WS                                     | 60   | IOZU-H              | word select input and output line of second baseband interface                                                               |  |

| Audio interface                                |      |                     |                                                                                                                              |  |

| HBCKOUT                                        | 65   | IOZU                | high-speed bit clock output[3]                                                                                               |  |

| I2S_I_BCK                                      | 75   | IOZU-H              | bit clock input and output line of I <sup>2</sup> S-bus input interface                                                      |  |

| I2S_I_SD                                       | 76   | IZU-H               | serial data input line of I <sup>2</sup> S-bus input interface                                                               |  |

| I2S_I_WS                                       | 74   | IOZU-H              | word select input and output line of I <sup>2</sup> S-bus input interface                                                    |  |

| I2S3_O_SD/<br>SPDIF_O                          | 73   | OL                  | serial data output line of third l <sup>2</sup> S-bus output interface; in alternative Sony/Philips digital output interface |  |

| 12S2_O_SD                                      | 72   | OL                  | serial data output line of second I <sup>2</sup> S-bus output interface                                                      |  |

| I2S1_O_BCK                                     | 66   | IOZU-H              | bit clock input and output line of first I <sup>2</sup> S-bus output interface                                               |  |

| I2S1_O_SD                                      | 68   | OL                  | serial data output line of first I <sup>2</sup> S-bus output interface                                                       |  |

| I2S1_O_WS                                      | 67   | IOZU-H              | word select input and output line of first I <sup>2</sup> S-bus output interface                                             |  |

<sup>[1]</sup> Table 15 defines the pin type.

<sup>[2]</sup> Required for seamless switching between digital and analog AM/FM modes in HD Radio applications under bad reception conditions.

<sup>[3]</sup>  $256 \times f_S$  output, required by some external DACs.

Table 8. Pin description (generic tuner interface)

| -             |     |                     |                                                                     |

|---------------|-----|---------------------|---------------------------------------------------------------------|

| Symbol        | Pin | Type <sup>[1]</sup> | Description                                                         |

| GPIO interfac | е   |                     |                                                                     |

| GPIO4         | 40  | IOZU                | general purpose input and output port 4                             |

| GPIO3         | 39  | IOZU                | general purpose input and output port 3                             |

| GPIO2         | 38  | IOZU                | general purpose input and output port 2                             |

| GPIO1         | 37  | IOZU                | general purpose input and output port 1                             |

| GPIO0         | 36  | IOZU                | general purpose input and output port 0                             |

| SPI3 interfac | е   |                     |                                                                     |

| SPI3_MISO     | 30  | IOZU-H              | master input, slave output of third SPI interface                   |

| SPI3_MOSI     | 31  | IOZU-H              | master output, slave input of third SPI interface                   |

| SPI3_SCLK     | 32  | IOZU-H              | serial clock input and output of third SPI interface                |

| SPI3_SS1_N    | 33  | IOZU-H              | slave select 1 input and output of third SPI interface (active LOW) |

| SPI3_SS2_N    | 35  | OZU                 | slave select 2 output of third SPI interface (active LOW)           |

<sup>[1]</sup> Table 15 defines the pin type.

Table 9. Pin description (SDRAM interface)

| Symbol            | Pin         | Type <sup>[1]</sup> | Description                  |

|-------------------|-------------|---------------------|------------------------------|

| Data input and ou | ıtput inter | face                |                              |

| SDRAM_DIO15       | 97          | IOL                 | data input and output bit 15 |

| SDRAM_DIO14       | 95          | IOL                 | data input and output bit 14 |

| SDRAM_DIO13       | 94          | IOL                 | data input and output bit 13 |

| SDRAM_DIO12       | 93          | IOL                 | data input and output bit 12 |

| SDRAM_DIO11       | 92          | IOL                 | data input and output bit 11 |

| SDRAM_DIO10       | 89          | IOL                 | data input and output bit 10 |

| SDRAM_DIO9        | 88          | IOL                 | data input and output bit 9  |

| SDRAM_DIO8        | 87          | IOL                 | data input and output bit 8  |

| SDRAM_DIO7        | 86          | IOL                 | data input and output bit 7  |

| SDRAM_DIO6        | 84          | IOL                 | data input and output bit 6  |

| SDRAM_DIO5        | 83          | IOL                 | data input and output bit 5  |

| SDRAM_DIO4        | 82          | IOL                 | data input and output bit 4  |

| SDRAM_DIO3        | 81          | IOL                 | data input and output bit 3  |

| SDRAM_DIO2        | 79          | IOL                 | data input and output bit 2  |

| SDRAM_DIO1        | 78          | IOL                 | data input and output bit 1  |

| SDRAM_DIO0        | 77          | IOL                 | data input and output bit 0  |

| Address output in | nterface    |                     |                              |

| SDRAM_AO12        | 126         | OZU                 | address output bit 12        |

| SDRAM_AO11        | 125         | OZU                 | address output bit 11        |

| SDRAM_AO10        | 123         | OZU                 | address output bit 10        |

| SDRAM_AO9         | 121         | OZU                 | address output bit 9         |

| SDRAM_AO8         | 120         | OZU                 | address output bit 8         |

| SDRAM_AO7         | 119         | OZU                 | address output bit 7         |

| SDRAM_AO6         | 118         | OZU                 | address output bit 6         |

Table 9.

Pin description (SDRAM interface) ...continued

| Symbol            | Pin | Type[1] | Description                                 |

|-------------------|-----|---------|---------------------------------------------|

| SDRAM_AO5         | 117 | OZU     | address output bit 5                        |

| SDRAM_AO4         | 115 | OZU     | address output bit 4                        |

| SDRAM_AO3         | 114 | OZU     | address output bit 3                        |

| SDRAM_AO2         | 113 | OZU     | address output bit 2                        |

| SDRAM_AO1         | 111 | OZU     | address output bit 1                        |

| SDRAM_AO0         | 110 | OZU     | address output bit 0                        |

| Control interface |     |         |                                             |

| SDRAM_BA1         | 104 | OZU     | bit 1 of bank address output                |

| SDRAM_BA0         | 103 | OZU     | bit 0 of bank address output                |

| SDRAM_CAS_N       | 108 | OZU     | column address selector output (active LOW) |

| SDRAM_CLK         | 127 | OZU     | clock output                                |

| SDRAM_CLKE        | 109 | OZU     | clock enable output                         |

| SDRAM_CLKIN       | 128 | IZU     | clock input for re-synchronization          |

| SDRAM_CS_N        | 105 | OZU     | chip select output (active LOW)             |

| SDRAM_DQM1        | 100 | OL      | MSByte of data qualifier mask output        |

| SDRAM_DQM0        | 99  | OL      | LSByte of data qualifier mask output        |

| SDRAM_RAS_N       | 106 | OZU     | row address selector output (active LOW)    |

| SDRAM_WE_N        | 98  | OZU     | write enable output (active LOW)            |

<sup>[1]</sup> Table 15 defines the pin type.

Table 10. Pin description (serial NOR-Flash interface)

| Symbol        | Pin | Type <sup>[1]</sup> | Description                                                |

|---------------|-----|---------------------|------------------------------------------------------------|

| SPI2 interfac | е   |                     |                                                            |

| SPI2_MI       | 16  | IZU                 | master input of second SPI interface                       |

| SPI2_MO       | 17  | OZD                 | master output of second SPI interface                      |

| SPI2_SCLK     | 18  | OZU                 | serial clock output of second SPI interface                |

| SPI2_SS1_N    | 19  | OZU                 | slave select 1 output of second SPI interface (active LOW) |

| SPI2_SS2_N    | 20  | OZU                 | slave select 2 output of second SPI interface (active LOW) |

| SPI2_SS3_N    | 22  | OZU                 | slave select 3 output of second SPI interface (active LOW) |

| SPI2_SS4_N    | 23  | OZU                 | slave select 4 output of second SPI interface (active LOW) |

<sup>[1]</sup> Table 15 defines the pin type.

Table 11. Pin description (external host microcontroller interface)

| Symbol                      | Pin      | Type[1]    | Description                                                                      |

|-----------------------------|----------|------------|----------------------------------------------------------------------------------|

| CLKOUT                      | 1        | OL         | clock output; clock source and clock frequency are programmable through software |

| RESET_N                     | 2        | IZU-H      | master reset input from host microcontroller (active LOW)                        |

| I <sup>2</sup> C-bus interf | ace (mas | ter and sl | ave)                                                                             |

| I2C2_DA                     | 9        | IOZD-H     | data acknowledge input and output of the I <sup>2</sup> C-bus interface 2        |

| I2C2_SCL                    | 7        | IOZU       | serial clock input and output of the I <sup>2</sup> C-bus interface 2            |

| I2C2_SDA                    | 8        | IOZU       | serial data input and output of the I <sup>2</sup> C-bus interface 2             |

| I2C1_DA                     | 5        | IOZD-H     | data acknowledge input and output of the I <sup>2</sup> C-bus interface 1        |

| I2C1_SCL                    | 3        | IOZU       | serial clock input and output of the I <sup>2</sup> C-bus interface 1            |

| I2C1_SDA                    | 4        | IOZU-H     | serial data input and output of the I <sup>2</sup> C-bus interface 1             |

| SPI1 interface              | Э        |            |                                                                                  |

| SPI1_SCLK                   | 12       | IZU-H      | serial clock input of first SPI interface                                        |

| SPI1_SI                     | 11       | IZU-H      | slave input of first SPI interface                                               |

| SPI1_SO                     | 10       | OL         | slave output of first SPI interface                                              |

| SPI1_SS_N                   | 13       | IZU-H      | slave select input of first SPI interface (active LOW)                           |

| <b>UART</b> interfa         | се       |            |                                                                                  |

| UART_CTS                    | 29       | IZU        | UART clear-to-send signal input                                                  |

| UART_RD                     | 25       | IZU        | UART receive data input                                                          |

| UART_RTS                    | 26       | ОН         | UART ready-to-send signal output                                                 |

| UART_TD                     | 24       | ОН         | UART transmit data output                                                        |

<sup>[1]</sup> Table 15 defines the pin type.

Table 12. Pin description (JTAG interface)

| Symbol | Pin | Type[1] | Description                                      |

|--------|-----|---------|--------------------------------------------------|

| TCK    | 132 | IZU     | test clock input                                 |

| TDI    | 135 | IZU     | test serial data input                           |

| TDO    | 136 | OL      | test serial data output                          |

| TMS    | 133 | IZU     | test mode select input                           |

| TRST_N | 131 | IZU     | test reset input; drive LOW for normal operating |

<sup>[1]</sup> Table 15 defines the pin type.

Table 13. Pin description (crystal oscillator)

| Symbol | Pin | Type <sup>[1]</sup> | Description                      |

|--------|-----|---------------------|----------------------------------|

| XTALI  | 141 | Al                  | crystal oscillator analog input  |

| XTALO  | 142 | AO                  | crystal oscillator analog output |

<sup>[1]</sup> Table 15 defines the pin type.

Table 14. Pin description (internally connected pins)

| Symbol | Pin             | Туре | Description                      |

|--------|-----------------|------|----------------------------------|

| i.c.   | 41,<br>43 to 54 | -    | internally connected; leave open |

Table 15. Pin type description

| Туре     | Description                                      | Unused pins <sup>[1]</sup>       |

|----------|--------------------------------------------------|----------------------------------|

| Generio  | pin types                                        |                                  |

| Al       | analog input pin                                 | always connect to quartz crystal |

| AO       | analog output pin                                | always connect to quartz crystal |

| G        | ground pin                                       | use all ground pins              |

| IOL      | digital input and output; drives LOW after reset | can be left open                 |

| IOZD     | digital input and output pin with weak pull-down | can be left open                 |

| IOZU     | digital input and output pin with weak pull-up   | can be left open                 |

| IZU      | digital input pin with weak pull-up              | can be left open                 |

| ОН       | digital output; drives HIGH after reset          | can be left open                 |

| OL       | digital output; drives LOW after reset           | can be left open                 |

| OZD      | digital output pin with weak pull-down           | can be left open                 |

| OZU      | digital output pin with weak pull-up             | can be left open                 |

| Р        | power supply pin                                 | use all power supply pins        |

| Specific | c pin types                                      |                                  |

| -H       | pins with hysteresis                             | see generic types                |

<sup>[1]</sup> Applications, which do not need all pins from SAF3560, can treat unused pins as indicated without damage or malfunction of the device.

# Terrestrial digital radio processor

# 7. Limiting values

Table 16. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                       | Parameter                                      | Conditions                                                                 |      | Min  | Max   | Unit |

|------------------------------|------------------------------------------------|----------------------------------------------------------------------------|------|------|-------|------|

| V <sub>DDA(OSC)(1V2)</sub>   | oscillator analog supply voltage (1.2 V)       |                                                                            |      | -0.5 | +1.7  | V    |

| V <sub>DDA(PLL)(1V2)</sub>   | PLL analog supply voltage (1.2 V)              |                                                                            |      | -0.5 | +1.7  | V    |

| V <sub>DDD(C)(1V2)</sub>     | core digital supply voltage (1.2 V)            |                                                                            |      | -0.5 | +1.7  | V    |

| V <sub>DDD(DAB)(3V3)</sub>   | DAB digital supply voltage (3.3 V)             |                                                                            |      | -0.5 | +3.9  | V    |

| V <sub>DDD(DSP)(3V3)</sub>   | DSP digital supply voltage (3.3 V)             |                                                                            |      | -0.5 | +3.9  | V    |

| V <sub>DDD(JTAG)(3V3)</sub>  | JTAG digital supply voltage (3.3 V)            |                                                                            |      | -0.5 | +3.9  | V    |

| V <sub>DDD(MC)(3V3)</sub>    | microcontroller digital supply voltage (3.3 V) |                                                                            |      | -0.5 | +3.9  | V    |

| V <sub>DDD(SDRAM)(3V3)</sub> | SDRAM digital supply voltage (3.3 V)           |                                                                            | -0.5 | +3.9 | V     |      |

| V <sub>DDD(MEM)(1V2)</sub>   | memory digital supply voltage (1.2 V)          |                                                                            |      | -0.5 | +1.7  | V    |

| T <sub>amb</sub>             | ambient temperature                            |                                                                            |      | -40  | +85   | °C   |

| T <sub>stg</sub>             | storage temperature                            |                                                                            |      | -65  | +150  | °C   |

| V <sub>ESD</sub>             | electrostatic discharge voltage                | human body model                                                           | [1]  | -    | ±2000 | V    |

|                              |                                                | charged device model                                                       | [2]  |      |       |      |

|                              |                                                | corner pins                                                                |      | -    | ±750  | V    |

|                              |                                                | other pins                                                                 |      | -    | ±500  | V    |

| l <sub>lu</sub>              | latch-up current                               | all supply voltages<br>below the maximum<br>values listed in this<br>table | [2]  | -100 | +100  | mA   |

<sup>[1]</sup> Class 2 according to JEDEC JESD22-A114.

## 8. Thermal characteristics

The SAF3560 has no special thermal requirements. The backside contact is needed for electrical reasons. For soldering considerations, see <u>Section 10</u>.

Table 17. Thermal characteristics

| Symbol        | Parameter                                   | Conditions  | Тур             | Unit |

|---------------|---------------------------------------------|-------------|-----------------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | <u>[1]</u> 26.3 | K/W  |

<sup>[1]</sup> The overall R<sub>th(j-a)</sub> is based on JEDEC conditions and can vary depending on the board layout. To minimize the effective R<sub>th(j-a)</sub> all power and ground pins must be connected to the power and ground layers directly. An ample amount of copper area directly under the SAF3560 with a number of through-hole plating, which connect to the ground layer (four-layer board: second layer), can also reduce the effective R<sub>th(j-a)</sub>. Do not use any solder-stop varnish under the chip. In addition the use of soldering glue with a high thermal conductance after curing is recommended.

<sup>[2]</sup> According to AEC-Q100-G.

#### Terrestrial digital radio processor

# 9. Package outline

Fig 4. Package outline SOT612-4 (HLQFP144)

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2010. All rights reserved.

# Terrestrial digital radio processor

# 10. Soldering

# Terrestrial digital radio processor

# 11. Abbreviations

Table 18. Abbreviations

| Table 18.            | Abbreviations                               |

|----------------------|---------------------------------------------|

| Acronym              | Description                                 |

| AEC                  | Automotive Electronics Council              |

| AM                   | Amplitude Modulation                        |

| BCK                  | Bit ClocK                                   |

| CA                   | Conditional Access                          |

| CD                   | Compact Disc                                |

| CGU                  | Clock Generation Unit                       |

| CTS                  | Clear To Send                               |

| DAB                  | Digital Audio Broadcasting                  |

| DAC                  | Digital-to-Analog Converter                 |

| DSP                  | Digital Signal Processor                    |

| EPG                  | Electronic Program Guide                    |

| FM                   | Frequency Modulation                        |

| GPIO                 | General Purpose Input and Output            |

| IF                   | Intermediate Frequency                      |

| I <sup>2</sup> C-bus | Inter-IC bus                                |

| $I^2S$               | Inter-IC Sound                              |

| I/O                  | Input/Output                                |

| JEDEC                | Joint Electronic Device Engineering Council |

| JTAG                 | Joint Test Action Group                     |

| MUX                  | MUltipleXer                                 |

| PLL                  | Phase-Locked Loop                           |

| RAM                  | Random Access Memory                        |

| RS232                | Recommended Standard 232[1]                 |

| RTS                  | Ready To Send                               |

| SD                   | Secure Digital memory card                  |

| SDR                  | Single Data Rate                            |

| SDRAM                | Synchronous Dynamic RAM                     |

| SPI                  | Serial Peripheral Interface                 |

| S/PDIF               | Sony/Philips Digital InterFace              |

| SRC                  | Sample-Rate Converter                       |

| UART                 | Universal Asynchronous Receiver Transmitter |

| WS                   | Word Select                                 |

|                      |                                             |

<sup>[1]</sup> A serial interface.

# Terrestrial digital radio processor

# 12. Revision history

# Table 19. Revision history

| Document ID     | Release date                      | Data sheet status                                         | Change notice        | Supersedes            |

|-----------------|-----------------------------------|-----------------------------------------------------------|----------------------|-----------------------|

| SAF3560_SDS v.3 | 20100915                          | Product short data sheet                                  | -                    | SAF3560_SDS v.2       |

| Modifications:  |                                   | of this data sheet has been red<br>of NXP Semiconductors. | designed to comply v | vith the new identity |

|                 | <ul> <li>Legal texts</li> </ul>   | have been adapted where app                               | ropriate.            |                       |

|                 | <ul> <li>Minor text of</li> </ul> | changes                                                   |                      |                       |

| SAF3560_SDS v.2 | 20100503                          | Product short data sheet                                  | -                    | -                     |

#### Terrestrial digital radio processor

# 13. Legal information

#### 13.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 13.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 13.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use in automotive applications** — This NXP Semiconductors product has been qualified for use in automotive applications. The product is not designed, authorized or warranted to be

suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

SAE3560 SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2010. All rights reserved.

## Terrestrial digital radio processor

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### 13.4 Licenses

#### ICs with HD Radio functionality

NXP Semiconductors ICs with HD Radio functionality are manufactured under license from iBiquity Digital Corporation. Sale or distribution of equipment that includes this device requires a license, which may be obtained at: iBiquity Digital Corporation, 6711 Columbia Gateway Drive, Suite 500, Columbia MD 21046, USA. Telephone: +1 (443) 539 4290, fax: +1 (443) 539 4291, e-mail: info@ibiquity.com.

#### 13.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

HD Radio — is a trademark of iBiquity Digital Corporation.

**HD Radio** — logo is a registered trademark of iBiquity Digital Corporation.

# 14. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

# Terrestrial digital radio processor

# 15. Contents

| 1    | General description         |

|------|-----------------------------|

| 2    | Features and benefits       |

| 2.1  | HD Radio technology         |

| 2.2  | Digital audio               |

| 2.3  | Memory                      |

| 2.4  | Other peripheral interfaces |

| 2.5  | Miscellaneous3              |

| 3    | Quick reference data        |

| 4    | Ordering information 4      |

| 5    | Block diagram 5             |

| 6    | Pinning information         |

| 6.1  | Pinning 6                   |

| 6.2  | Pin description             |

| 7    | Limiting values             |

| 8    | Thermal characteristics 13  |

| 9    | Package outline             |

| 10   | Soldering                   |

| 11   | Abbreviations               |

| 12   | Revision history            |

| 13   | Legal information           |

| 13.1 | Data sheet status           |

| 13.2 | Definitions                 |

| 13.3 | Disclaimers                 |

| 13.4 | Licenses                    |

| 13.5 | Trademarks19                |

| 14   | Contact information 19      |

| 15   | Contents                    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2010.

All rights reserved.